AND Gate

The AND/NAND Gate models a generic AND or NAND gate with up to nine inputs. The number of active-low inputs can be set to one less than the total number of inputs. Both AND and NAND outputs are provided. The outputs change state at the same time, making the outputs perfectly complementary.

To implement a logic gate with more than nine inputs, see Digital Lookup Table and Digital Lookup Table with Don't Care in Input Definitions.

In this topic:

| Model Name: | AND/NAND Gate | |||

| Simulator: |  |

This device is compatible with the SIMPLIS simulator. | ||

| Parts Selector Menu Location: | ||||

| Symbol Library: | None - the symbol is automatically generated when placed or edited. | |||

| Model Library: | SIMPLIS_DIGI1.LB | |||

| Subcircuit Names: |

The "X" in each subcircuit name is an integer from 2 to 9 representing the total number of inputs. For example, SIMPLIS_DIGI1_AND3_N is a 3-input AND/NAND gate. |

|||

| Symbol: |

|

|||

| Multiple Selections: | Only one device at a time can be edited. | |||

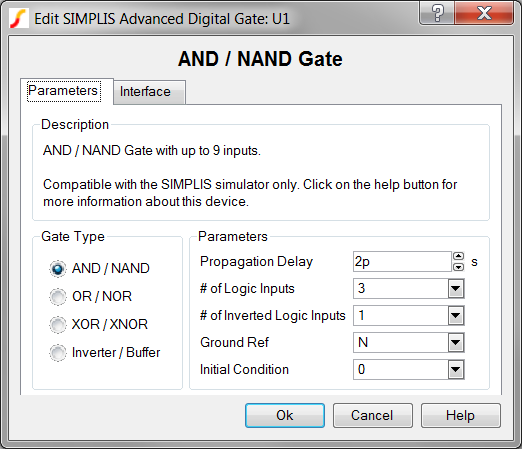

Editing the AND/NAND Gate

To configure the AND/NAND Gate, follow these steps:

- Double click the symbol on the schematic to open the editing dialog to the Parameters tab.

- Make the appropriate changes to the fields described in the table below the image.

| Label | Parameter Description |

| Propagation Delay | Delay from when any input pin changes state until the outputs change state |

| # of Logic Inputs | Number of active-high logic inputs |

| # of Inverted Logic Inputs | Number of active-low logic inputs. Any device can have active-low inputs up to the # of Logic Inputs minus 1. |

| Ground Ref | Determines whether or not a device has a ground reference pin. Any digital component that has an input or output pin connected to an analog circuit node must have its Ground Ref pin connected to an analog node. This is usually the ground on the schematic. |

| Initial Condition | Initial condition of the Gate output at time=0 |

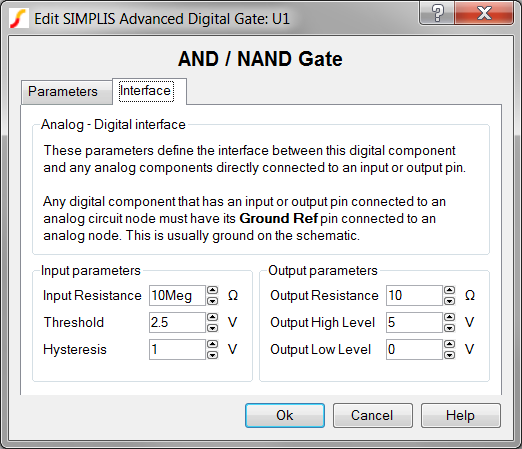

To define the parameters for the interface between this digital component and each analog component connected directly to an input or output pin, follow these steps:

- From the Edit AND/NAND Gate dialog box, click on the Interface tab.

- Make the appropriate changes to the fields described in the table below the image.

| Label | Parameter Description | |||||||

| Input Resistance | Input resistance of each Gate input pin | |||||||

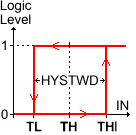

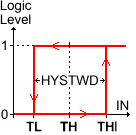

| Hysteresis, Threshold |  |

Hysteresis and

Threshold of the inputs. The hysteretic-window width, HYSTWD

is centered around Threshold (TH) voltage. To

determine the actual threshold ( TL , THI ),

substitute Threshold (TH) and Hysteresis

(HYSTWD) in each of the following formulas:

|

||||||

| Output Resistance | Output resistance of each Gate output pin | |||||||

| Output High Voltage | Output high voltage for each Gate output pin | |||||||

| Output Low Voltage | Output low voltage for each Gate output pin | |||||||

Truth Table

The following truth table is for a two input AND/NAND Gate with active-high inputs.

| Inputs | Outputs | ||

| A | B | AND | NAND |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Examples

The test circuit used to generate the waveform examples in the next section can be downloaded here: simplis_056_andgate_example.sxsch.

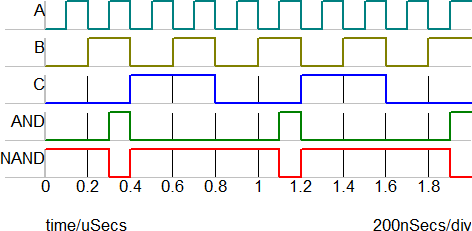

Waveforms

The waveforms below were taken from a 3-input gate with two active-high inputs and one active-low input. The two active-high inputs are labeled A and B, and the active-low input is labeled C. With these connections, the AND output will be high when A and B inputs are high and the C input is low.

Subcircuit Parameters

X$U1 6 9 2 3 4 SIMPLIS_DIGI1_AND3_N vars: NumInv=1 IC=0 RIN=10Meg ROUT=10 HYSTWD=1 VOL=0 VOH=5 DELAY=2p TH=2.5

| Parameter Name | Label | Data Type | Range | Units | Parameter Description | |||||||

| DELAY | Propagation Delay | Number | 1f to 1024 | s | Delay from when any input pin changes state until the outputs change state | |||||||

| GNDREF | Ground Ref | String |

|

none | Determines whether or not a device has a ground reference pin. Any digital component that has an input or output pin connected to an analog circuit node must have its Ground Ref pin connected to an analog node. This is usually the ground on the schematic. | |||||||

| HYSTWD, TH |

Hysteresis, Threshold |

Number | min: 1f | V |  |

Hysteresis and Threshold of

the inputs. The hysteretic-window width, HYSTWD is centered

around Threshold (TH) voltage. To determine the actual

threshold ( TL , THI ), substitute Threshold

(TH) and Hysteresis (HYSTWD) in each of the

following formulas:

|

||||||

| IC | Initial Condition | Number |

|

none | Initial condition of the Gate output at time=0 | |||||||

| NUMINV | # of Inverted Logic Inputs | Number |

|

none | Number of active-low logic inputs. Any device can have active-low inputs up to the # of Logic Inputs minus 1. | |||||||

| NUMNONINV | # of Logic Inputs | Number |

|

none | Number of active-high logic inputs | |||||||

| RIN | Input Resistance | Number | min: 100 | Ω | Input resistance of each Gate input pin | |||||||

| ROUT | Output Resistance | Number | min: 1m | Ω | Output resistance of each Gate output pin | |||||||

| VOH | Output High Voltage | Number | any | V | Output high voltage for each Gate output pin | |||||||

| VOL | Output Low Voltage | Number | any | V | Output low voltage for each Gate output pin | |||||||