# Coupled-Inductor Design Optimization for Fast-Response Low-Voltage DC-DC Converters

Jieli Li Charles R. Sullivan Aaron Schultz Thayer School of Engineering, Dartmouth College Jieli.Li@dartmouth.edu Charles.R.Sullivan@dartmouth.edu

Abstract—Multiphase voltage regulator modules (VRMs) for microprocessor power delivery with coupled output inductors are discussed. Strong coupling is shown to be feasible and effective at reducing ripple if the correct magnetic topology is used. For more than two phases, this can be a "ladder" core with windings around each rung. Typical ripple reduction is better than a factor of six with no effect on response time. One can also chose to improve response time while still significantly reducing ripple. A simultaneous numerical optimization of the magnetics and the circuit is used to minimize loss in a fast-response 100 A design.

# I. INTRODUCTION

High-current low-voltage power converters with fast response are needed for powering digital systems such as microprocessors, which are projected to require 100 A or more at under 1 V [1]. What makes this application particularly challenging is that the load current can step from near zero to full load or vice versa in a matter of nanoseconds, and the voltage must be held stable throughout the step, with a projected tolerance of less than 50 mV [1]. The combination of high current and fast response requires a voltage regulator module (VRM) located immediately adjacent to the load. The VRM must be small in size as well as have high efficiency and extremely fast response.

Presently, the standard design used for high-performance VRMs is a buck converter with multiple parallel sections, staggered in phase [2], [3], [4], [5], [6], [7]. In a buck converter with a load-current step, the output capacitor supplies (or sinks) the immediate difference in current while the inductor current is ramped up or down to match the new load current. A small inductor allows ramping the current quickly to minimize the output capacitor requirement. However, small inductor values also lead to large ripple current. In a single-phase converter, large ripple current in the inductor increases the output capacitor requirement when the inductor is very small [6], [7]. The standard multiphase interleaved design avoids this problem because it achieves substantial ripple current cancellation in the output capacitor. This allows smaller inductance without requiring a large output capacitor. However, the full ripple current flows through the MOSFET switches (including synchronous rectifiers) and through the inductor itself, resulting in higher losses and higher peak current requirements. One strategy to reduce the ripple current throughout is to operate at very high switching frequencies (e.g., see [6]), but this increases switching and gate-drive losses and imposes difficult requirements for magnetic materials capable of low loss at very high frequencies.

In [8], [9], it was shown that coupling the inductors in a

two-phase interleaved converter can effect a reduction in ripple. Unlike the ripple cancellation in an uncoupled multiphase converter, this ripple reduction extends to the current in the inductor windings and in the switches. In [10], one topology for coupling larger numbers of inductors in a multiphase VRM is considered, but is not found to offer major advantages.

In this paper, we show that coupled inductors can be used to obtain significantly greater performance improvements than those obtained in [8], [9], [10]. For two-phase converters, we show that a different gapping configuration leads to higher ripple reduction, and we present a simple explanation of the circuit behavior in the limit of ideal coupling. For multiphase (more than two phases) coupling, we introduce a new topology that allows practical operation with much stronger coupling than is possible with the topology in [10], and thus allows greatly reducing ripple while simultaneously improving transient response.

In order to most effectively apply the new multiphase topology, we have developed a simultaneous optimization of the circuit and the coupled inductor structure. The calculation of performance used for the optimization is described in Section IV, and the results of the optimization are given in Section V.

## II. TWO-PHASE COUPLING

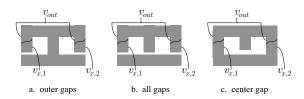

For the purpose of economizing on magnetic material and reducing the loss in the magnetic material, it is possible to share a core leg between two inductors in a two-phase buck converter. If a high-permeability ungapped leg is shared, as shown in Fig. 1a, the coupling between the two windings is very small, and it is possible to reduce the amount of magnetic material required without affecting circuit performance. With the phases oriented as shown in Fig. 1, the ac flux is reduced in the center leg, and so are the losses, but the dc flux requirement for that leg is increased [9], [8]. These effects are of minor importance, because the center leg is a small portion of the overall core volume.

More interesting is the configuration shown in Fig. 1b with gaps in all of the legs. The phases then become coupled, resulting in a moderate ripple reduction [9], [8]. However, the strongly-coupled configuration in Fig. 1c is capable of producing greater ripple reduction. With high permeability core material, at low duty cycles the coupling approximately cuts ripple current in half for the same transient response. As duty cycle increases towards 50%, the ripple is reduced further and approaches zero with 50% duty cycle and very high perme-

Fig. 1. Alternative gapping configurations for two-phase coupled inductor. The voltages  $v_x$  are the switching node waveforms for each phase, as in Fig. 2.

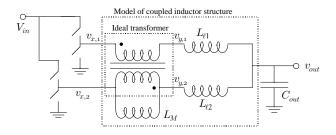

Fig. 2. Model for two-phase coupled buck converter.

ability core material.

An electrical circuit model for this coupled structure can be easier to understand than a magnetic circuit model. The circuit shown in Fig. 2, with leakage inductances  $L_{\ell 1}$  and  $L_{\ell 2}$ , an ideal transformer, and a single magnetizing inductance  $L_M$ , can be used to model any linear magnetic structure with two windings. With equal numbers of turns on the two windings, as with all the structures in Fig. 1, the ideal transformer has a 1:1 turns ratio. The gapping configurations and gap lengths affect the values of  $L_{\ell 1}$  and  $L_{\ell 2}$  (which are equal by symmetry) and  $L_M$ ; this circuit model can be used to analyze the behavior for any set of these values. However, the circuit in Fig. 2 is easiest to understand when we consider Fig. 1c. In this configuration, the magnetizing inductance is proportional to the permeability of the core. For the purpose of a qualitative understanding of the circuit, we can consider the case in which the permeability approaches infinity such that the magnetizing inductance is approximately an open circuit for any ac currents or voltages.

To make a fair comparison with the uncoupled case, we consider equal energy storage in nominal dc conditions. Because the magnetizing inductance's energy storage is negligible when the magnetizing path is ungapped, equal energy storage implies that the values of the leakage inductances  $L_{\ell 1}$ and  $L_{\ell 2}$  are equal to the values of the uncoupled inductors.

With no magnetizing inductor, the ideal transformer (with the polarity as shown) forces the ac currents in the two phases to be equal. Thus the ac currents in the two leakage inductances,  $L_{\ell 1}$  and  $L_{\ell 2}$ , are also equal, assuming that (by symmetry) the leakage inductances are equal. With equal ac currents, the leakage inductances also have identical voltages across them. Thus, the voltages at the nodes labeled  $v_{y1}$  and  $v_{y2}$  must match. The transformer equation requires  $v_{x1} - v_y = v_y - v_{x2}$ ,

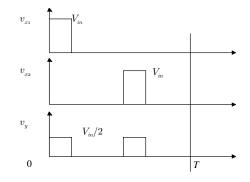

Fig. 3. Waveforms for the circuit in Fig. 2. The two  $v_y$  nodes have identical waveforms, shown in the bottom plot.

where we have dropped the index on the  $v_y$ 's because they are equal. Given  $v_{x1}$  and  $v_{x2}$  from the switching configuration, we can find  $v_y = (v_{x1} + v_{x2})/2$ : the voltages  $v_y$  are equal to the average of the voltages at the  $v_x$  nodes. Thus, for example, for small duty cycles, each  $v_x$  pulses to  $V_{in}$  once per cycle. Because they are equal to the average of the  $v_x$ 's, the  $v_y$ 's pulse to  $V_{in}/2$  twice per cycle, as shown in Fig. 3.

For the leakage inductances, this is like having a converter running from a input voltage  $V_{in}/2$ , switching at twice the actual switching frequency  $f_s$ . The on-time is unchanged, but the apparent duty cycle is twice the original duty cycle, so that the output voltage is the same as without coupling.

To evaluate the ripple with perfect coupling  $(L_M \to \infty)$ , consider that the ripple in a standard buck converter is proportional to  $(1 - D)/f_s$ . With both the effective duty cycle and the effective frequency doubled, the ratio of ripple current with coupling to ripple current without coupling (using inductors equal to  $L_\ell$ ) is

$$\frac{I_{pp,coup}}{I_{pp,uncoup}} = \frac{(1-2D)/(2f_s)}{(1-D)/f_s} = \frac{(1/2-D)}{(1-D)}.$$

(1)

This circuit in Fig. 2 can also be used to derive the waveforms with finite magnetizing inductance. This analysis is not shown here because it leads to expressions for ripple in the case of imperfect coupling that are equivalent to those in [9], and because it is a special case of the more general analysis we present in Section IV.

Strong coupling can substantially reduce the ripple in the steady-state waveforms. Now consider the effect on transient response. During recovery from a load transient, the controller should simultaneously activate either both high-side switches or both low-side switches (synchronous rectifiers). In this case, the ideal transformer does nothing, as the voltages at the two  $v_x$  nodes are equal to each other and equal to the voltages at the two  $v_y$  nodes. So the transient response is determined exclusively by the leakage inductances  $L_{\ell 1}$  and  $L_{\ell 2}$ , and is identical to the transient response with uncoupled inductors sized to match the leakage inductances (the same sizing that gives equal energy storage, as discussed above). Since

the coupling does not affect the circuit behavior when all the phases are switched together, the analysis of transient response is virtually identical to the analysis of transient response in uncoupled multiphase converters [4], [7], [6], [11], [12], and does not require further discussion here.

Another way to think about the operation of this magnetic structure is in terms of common-mode and differential-mode inductances. We want the differential mode inductance high in order to reduce ripple associated with the differences between the ac voltages at each  $v_x$  node. At the same time, we want the common mode inductance to be low for fast response when the phases all switch together in a transient condition. The configuration in Fig. 1c is similar to the standard common-mode choke used to reduce conducted EMI, but with the winding polarities flipped to maximize differential mode inductance instead of common-mode inductance. As in a standard commonmode choke, the gapped center leg is not necessary; without that leg present, a small leakage inductance results from the air paths between the top and bottom core legs and will often still provide sufficient leakage inductance. In a common-mode choke, the equal and opposite low-frequency currents allow the use of high permeability core material without saturation. In the configuration in Fig. 1c, the opposite winding polarity allows large dc currents in each phase without saturation as long as the dc currents are equal.

# III. NEW TOPOLOGY FOR MULTIPHASE COUPLING

The advantages of the coupled inductor in Fig. 1c may be extended to inductors with any number of phases. It is not immediately clear how to do this, as it is possible to construct magnetic circuits with multiple windings (transformers) with the winding branches in parallel or in series [13], or in other configurations such as in [10]. The effect that we want from the transformer aspect of the device (the ideal transformer portion of the model in Fig. 2) is to balance the phase currents. With the ac current in all the leakage inductances equal, it follows that the voltages  $v_{y}$  must be equal, and hence equal to the average of the voltages  $v_x$ . The multiwinding transformer configuration that enforces equal currents is with the winding branches in parallel. With a high-permeability core, the parallel branches must all have the same MMF across them, and so the Ni product must be the same for each. With equal numbers of turns N, the current must be equal. This is in contrast to a conventional multiwinding transformer with the winding branches in series (or all the windings on the same leg) which enforces equal v/N on each winding, and requires that  $\Sigma N i = 0$  [13].

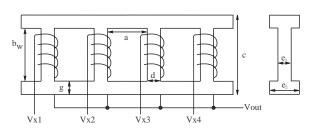

Thus, we want to configure the winding branches in parallel in order to force the currents to match as closely as possible. The core can be a ladder structure, as shown in Fig. 4, which is drawn without the optional gapped center legs shown in Fig 1c—the leakage flux paths serve the same purpose. With the windings placed on the rungs of the ladder (rather than on the outer legs as in [10]), the advantage of avoiding saturation

Fig. 4. New topology for multi-phase coupled inductors, shown for four phases. The placement of windings on the rungs of the ladder core structure, instead of on the outer legs, allows the use of high-permeability material for high coupling, without the dc current (equal in each winding) producing saturation.

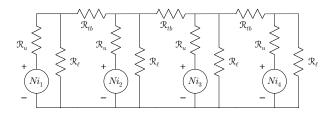

Fig. 5. Magnetic circuit model for four-phase coupled inductor.  $\mathcal{R}$  is the reluctance of a given path:  $\mathcal{R}_{\ell}$  is the leakage reluctance,  $\mathcal{R}_{tb}$  is the sum of the reluctances of top and bottom outer legs across any one window, and  $\mathcal{R}_u$  is the reluctance of the rung (post around which the wire is wound). The MMF source Ni corresponds the the current and number of turns in the corresponding winding.

with equal dc currents in all the windings is retained. With equal currents, the MMF produced by each winding is equal, and the only flux circulation induced is through leakage paths through the air. Fig. 5 shows a magnetic circuit for this structure.

#### IV. CALCULATING PERFORMANCE

# A. Model Formulation

Formulating a model in terms of a matrix equation will facilitate developing an analysis that applies to any number of phases. Based on Fig. 5 we can write

$$\Phi_u = \mathbf{A}\mathcal{F},\tag{2}$$

where  $\Phi_u$  is a vector containing the magnetic flux in each rung of the ladder structure,  $\mathcal{F}$  is a vector of the MMF values at each node at the top of Fig. 5, and, for four phases,

$$\mathbf{A} = \begin{bmatrix} \frac{1}{\mathcal{R}_{tb}} + \frac{1}{\mathcal{R}_{\ell}} & -\frac{1}{\mathcal{R}_{tb}} & 0 & 0\\ -\frac{1}{\mathcal{R}_{tb}} & \frac{2}{\mathcal{R}_{tb}} + \frac{1}{\mathcal{R}_{\ell}} & -\frac{1}{\mathcal{R}_{tb}} & 0\\ 0 & -\frac{1}{\mathcal{R}_{tb}} & \frac{2}{\mathcal{R}_{tb}} + \frac{1}{\mathcal{R}_{\ell}} & -\frac{1}{\mathcal{R}_{tb}}\\ 0 & 0 & -\frac{1}{\mathcal{R}_{tb}} & \frac{1}{\mathcal{R}_{tb}} + \frac{1}{\mathcal{R}_{\ell}} \end{bmatrix},$$

(3)

The matrix **A** may be similarly expressed for any number of phases. Using

$$\Phi_u = \frac{Ni - \mathcal{F}}{\mathcal{R}_u},\tag{4}$$

we can find an expression for the vector of currents in each winding as a function of the vector of flux in each rung,

$$i = \frac{1}{N} (\mathcal{R}_u + A^{-1}) \Phi_u.$$

(5)

## B. Calculation of Steady-State Waveforms

Using the model derived above, we wish to calculate magnetic flux waveforms and current waveforms; both have dc components and ac components which we calculate separately.

The dc components are calculated by assuming that the dc currents in each phase are equal. This is necessary for proper operation, and may be achieved by the same active or passive methods that are used for uncoupled multiphase converters. Thus, if we have total current in the load  $I_{total}$  and the number of phases is n, the dc component of current in each phase is  $I_{phase,dc} = I_{total}/n$ . The dc component of flux in the outside legs of the ladder core (top and bottom in Fig. 4) is zero and the flux in each rung is

$$\Phi_{u,dc} = \frac{NI_{phase,dc}}{\mathcal{R}_u + \mathcal{R}_\ell}.$$

(6)

With the switches operated with duty cycle D, the voltage across each winding will switch from  $V_{in}$  to zero. The relationship between the flux change in the rung and the voltage is

$$V = -N\frac{d\Phi_u}{dt} \tag{7}$$

From the duty cycle and the period, we can obtain the ac component of flux in the rung. From equation (5), we can calculate the ac components the winding currents. The ac component of the MMF  $\mathcal{F}$  can be found by inverting (2); the MMF can then be used to calculate flux in the outside legs of the ladder core (top and bottom in Fig. 4) using

$$\Phi_{tb} = \frac{\Delta \mathcal{F}}{\mathcal{R}_{tb}}.$$

(8)

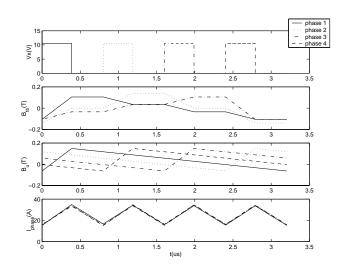

Now we have all the components of fluxes and currents. Example waveforms are shown in Fig. 6, for the parameters shown in Table I. The strong coupling makes the current waveforms in the four phases virtually indistinguishable. The current ripple of about 20 A peak-to-peak looks large, making one wonder how effective the coupling is at reducing ripple, but this design takes advantage of the coupling effect to operate at a relatively low frequency (312 kHz), while having the low leakage (common mode) inductance that would normally only be feasible with a switching frequency above 1 MHz. If this design was operated at the same frequency (312 kHz) with no coupling, the peak-to-peak current ripple would be 123 A in each phase, over six times higher.

Fig. 6. Example waveforms calculated as described in the text for the fourphase coupled-inductor converter with the parameters specified in Table I. Shown for each phase are: switching-node voltages  $v_x$ , outer core leg fluxes  $\Phi_{tb}$ , core rung fluxes  $\Phi_u$ , and phase currents *i*.

TABLE I

Design Parameters for Example Waveforms.

| Symbol         |                                                 | Value       |

|----------------|-------------------------------------------------|-------------|

| $V_{in}$       | Input voltage                                   | 12 V        |

| $V_{out}$      | Output voltage                                  | 1.45 V      |

| $I_{total}$    | Total output current                            | 100 A       |

| $L_{\ell,tot}$ | Parallel combination of all leakage inductances | 8.25 nH     |

| n              | Number of phases                                | 4           |

| N              | Number of winding turns                         | 3           |

| $f_s$          | Switching frequency                             | 312 kHz     |

|                | Core material                                   | Magnetics K |

|                | Geometrical parameters, as defined in Fig. 4    | (mm)        |

|                | a                                               | 1.34        |

|                | $b_w$                                           | 24.3        |

|                | с                                               | 28.0        |

|                | d                                               | 3.86        |

|                | $e_1$                                           | 1.66        |

|                | $e_2$                                           | 3           |

|                | g                                               | 1.84        |

## C. Calculation of Power Loss

There are three parts of power loss that we consider in our analysis: winding loss, magnetic core loss, and loss in the remainder of the circuit.

With high-frequency current, winding loss increases because of eddy-current effects [14]. However, with strong coupling, the ripple current can be small, which means that neglecting this effect will not lead to major errors. Thus, we calculate winding loss using simply the total rms current and the dc resistance,  $P_w = I_{rms}^2 R_{dc}$ .

For the calculation of the core in ferrites, the Steinmetz equation is often used:

$$P_v = k f^{\alpha} \hat{B}^{\beta}, \tag{9}$$

where k,  $\alpha$ ,  $\beta$  are constants often given by the manufacturer of the magnetic material,  $P_v$  is power loss per unit volume,  $\hat{B}$ is peak flux density, and f is the frequency of sinusoidal excitation. Unfortunately, the Steinmetz equation applies directly only for sinusoidal waveforms. While it may be an adequate approximation for symmetric triangular flux waveforms, it is not adequate for extreme duty cycles (for example, in a 12 V to 1 V converter) [15], much less for the unusual irregular waveforms that appear in some legs of the coupled inductor. Note that separating the waveform into sinusoidal components via Fourier analysis and calculating the loss separately for each component does not work because the loss mechanism is non-linear.

To solve this problem, we use the "Generalized Steinmetz Equation" (GSE) method introduced in [16] for analyzing for losses with arbitrary nonsinusoidal waveforms. The GSE finds the time average core loss per unit volume  $\overline{P_v}$  as

$$\overline{P}_v = \frac{1}{T} \int_0^T k_1 |(dB/dt)|^{\alpha} |B(t)|^{\beta-\alpha} dt \qquad (10)$$

where  $\alpha$ ,  $\beta$  are the same as in (9) and

$$k_1 = \frac{k}{(2\pi)^{\alpha-1} \int_0^{2\pi} |\cos\theta|^{\alpha} |\sin\theta|^{\beta-\alpha} d\theta}.$$

(11)

The effectiveness of the GSE was experimentally verified in [16].

Applying the GSE to a general periodic piece-wise-linear waveform, we obtain

$$\overline{P}_{v} = \frac{k_{1}}{T(\beta - \alpha + 1)} \sum \left| \frac{B_{i+1} - B_{i}}{t_{i+1} - t_{i}} \right|^{\alpha - 1} |B_{i+1}^{\beta - \alpha + 1} - B_{i}^{\beta - \alpha + 1}|$$

(12)

where  $B_i$  are the flux densities at times  $t_i$ . For (12), B is assumed to always be greater than or equal to zero. If B crosses the line of B = 0, we convert the negative part to its absolute value before applying (12).

In addition to the loss in the inductor itself, the calculations and optimizations take into account circuit losses. Losses in the output-capacitor ESR are neglected, assuming that ripple cancellation reduces them to near zero, and that ripple cancellation and fast response allow the use of low-ESR ceramic capacitors. Thus, we consider only losses in the MOS-FET switches. We assume fixed total switching loss per cycle  $E_{switch}$ , including gate drive loss, and fixed total parallel resistance of the high side switches (considered in parallel) and of the low side switches. The values of these parameters used in the example optimization in Section V are based on datasheet parameters of low-gate-charge commercial MOSFETs (STB70NF03L), and are listed in Table II. These numbers are scaled by the number of phases to find parameters for a given phase-resistance for a given phase is scaled up by the number of phases and switching loss is scaled down. The idea of this is that the overall numbers represent many parallel MOSFETs, and that the total number of MOSFETs stays fixed as we change the number of phases. In practice, an integer number of MOSFETs must be allocated to each

TABLE II PARAMETERS FOR OPTIMIZATION

| Symbol         |                                                    | Value                   |

|----------------|----------------------------------------------------|-------------------------|

| $V_{in}$       | Input voltage                                      | 12 V                    |

| $V_{out}$      | Output voltage                                     | 1.45 V                  |

| $I_{total}$    | Total output current                               | 100 A                   |

| $L_{\ell,tot}$ | Parallel combination of all leakage inductances    | 8.25 nH                 |

| $E_{switch}$   | Total switching loss per cycle for all phases      | 5.79 μJ                 |

| $R_{n,tot}$    | On-resistance of all low-side switches in parallel | 0.8 mΩ                  |

| $R_{p,tot}$    | On-resistance of high-side switches in parallel    | $2.16 \mathrm{m}\Omega$ |

| $e_2$          | Maximum height allowed                             | 3 mm                    |

| A              | Maximum footprint area                             | $582 \text{ mm}^2$      |

|                | Core material                                      | Magnetics K             |

|                | Parameters for core material: Magnetics K material | MKS units               |

| k              | Core loss constant for (9)                         | 0.759                   |

| α              | Core loss frequency exponent                       | 1.565                   |

| β              | Core loss flux density exponent                    | 2.759                   |

| $k_1$          | Core loss constant for (10)                        | 0.192                   |

| $\mu_r$        | Relative permeability of core material             | 1500                    |

phase, but we allow the switch parameters to vary continuously. We believe this analysis is more useful than constraining the results to integer numbers of available MOSFETs in parallel because it allows us to see the underlying design issues. For practical application, one could then modify the results to find what works best with presently available device sizes, or work with a MOSFET manufacturer to produce the size device needed. The parameters in Table II are based on using ten of the STB70NF03L is parallel for the low-side switch, and using a smaller, non-integer number (3.7) in parallel for the high-side switch, scaled down for the lower rms current.

Rather than fixing the total number of parallel MOSFETs, we could choose to select the number to minimize total loss including switching and gate-drive loss and conduction loss. This would give lower-loss designs than the ones we report, but in practice the number and size of MOSFETs used is limited by cost.

To calculate conduction losses, an effective on-resistance of

$$R_{on,eff} = DR_p + (1 - D)R_n \tag{13}$$

is multiplied by the square of the rms current. The switching loss energy, scaled by the current, is simply multiplied by switching frequency to find switching loss power.

## V. OPTIMIZATION

Given a complete method for calculation of performance, as described in Section IV, standard numerical optimization algorithms can be used to find the optimum values for a set of free parameters, given fixed values for the other parameters. We used the Nelder-Mead simplex algorithm as implemented in the MATLAB function fminsearch [17].

The parameters for which we have run the optimization are listed in Table II. Fixed optimization parameters include the technology and number of parallel MOSFETs as discussed in Section IV, the size of the magnetic structure, and the electrical parameters of the converter. The footprint area of the

| n            | Number of coupled phases  | 1    | 2    | 3    | 4    | 5    | 6    | 7    |     |

|--------------|---------------------------|------|------|------|------|------|------|------|-----|

| N            | Number of turns           |      | 2    | 2    | 3    | 3    | 3    | 3    |     |

| a            | Window                    |      | 1.35 | 1.28 | 1.34 | 1.29 | 1.25 | 1.21 | mm  |

| $b_w$        | Window breadth            |      | 32.7 | 22.1 | 24.3 | 19.6 | 16.7 | 14.7 | mm  |

| c            | Device breadth            |      | 36.0 | 26.5 | 28.0 | 23.8 | 21.2 | 19.4 | mm  |

| d            | Rung width                |      | 6.72 | 6.03 | 3.86 | 3.60 | 3.32 | 3.06 | mm  |

| $e_1$        | Rung thickness            |      | 1.65 | 1.72 | 1.66 | 1.71 | 1.75 | 1.79 | mm  |

| $e_2$        | Height                    |      | 3    | 3    | 3    | 3    | 3    | 3    | mm  |

| g            | Outer leg                 |      | 1.65 | 2.24 | 1.84 | 2.10 | 2.26 | 2.36 | mm  |

| $f_s$        | Switching freq.           | 872  | 525  | 387  | 312  | 281  | 279  | 295  | kHz |

| $I_{ac,rms}$ | Total rms ripple current* | 51.1 | 36.9 | 28.1 | 21.2 | 14.5 | 8.85 | 4.50 | А   |

| $P_w$        | Winding loss              |      | 0.69 | 0.95 | 1.37 | 1.65 | 1.90 | 2.12 | W   |

| $P_c$        | Core loss                 |      | 0.47 | 0.74 | 0.92 | 1.21 | 1.48 | 1.73 | W   |

| $P_L$        | Total Inductor Loss       |      | 1.16 | 1.69 | 2.29 | 2.86 | 3.38 | 3.85 | W   |

| $P_s$        | Switching loss            | 5.05 | 3.04 | 2.24 | 1.81 | 1.63 | 1.61 | 1.70 | W   |

| $P_{rds}$    | MOSFET conduction loss    | 12.2 | 11.0 | 10.4 | 10.1 | 9.85 | 9.72 | 9.66 | W   |

| $P_M$        | Total MOSFET loss         | 17.2 | 14.0 | 12.6 | 11.9 | 11.5 | 11.3 | 11.4 | W   |

| $P_t$        | Total loss                |      | 15.2 | 14.3 | 14.2 | 14.3 | 14.7 | 15.2 | W   |

TABLE III

Optimization Results for 100 A 12 V to 1.45 V Converter

\*The sum of ac rms currents in each phase.

magnetic structure is fixed at 582 mm<sup>2</sup>, based on an estimate of the area that would be required for a conventional discrete-inductor design for 100 A. The inductor performance is strongly affected by height. This optimization was performed for a maximum height of 3 mm; allowing a thicker device could rapidly cut inductor loss and/or area, although inductor loss turns out to be a small fraction of the total loss. The output voltage of 1.45 V was chosen to be in the range of interest, and to be a value that doesn't have any simple integer relationship with the input voltage of 12 V. The total output current is fixed at 100 A, and the per-phase current is adjusted according to the number of phases used. Thus, for example, for four phases, the per-phase current is 25 A.

The coupled inductor system allows improving response time for the same level of ripple current, or decreasing ripple for the same fixed response time. In these optimizations, we fixed response time, by fixing the total parallel inductance for the 100 A output to allow a current slew rate in the inductors faster than any existing VRM we know of, thus minimizing the output capacitance requirement. We assumed initially that the appropriate leakage inductance would be achieved through air paths and widening of the outer core legs. Because the optimization resulted in long, thin rungs, it is likely that additional core legs will be needed in practice to achieve the necessary leakage inductance. The most practical way to implement that is a topic for future study.

With the constraints discussed above set, there remain six degrees of freedom to be adjusted for minimum loss. These could be expressed in various linearly-related sets of parameters; we used cross-sectional area of the core in two different places (the rung and the outer leg), the thickness of the rung  $(e_1 \text{ in Fig. 4})$ , the switching frequency, the number of turns on each phase, and the number of phases.

We find that changing the relationship between the physi-

cal and electrical ordering of the phases can help reduce current ripple. The idea is that a large phase difference between nearby phases will improve the ripple cancellation effect compared to putting phases in order, which would make adjacent phases have relatively small phase differences. For small numbers of phases, optimal phase orders can easily be found by inspection. For example, [1 3 2 4] is the optimal ordering for four phases; [1 3 5 2 4] for five. For large numbers of phases, we have not yet found a way to determine the optimum phase order, but we have used our best guesses of good phase ordering. In designs with an ungapped, high-permeability core, the coupling between any two phases is good enough that the phase order makes very little difference, especially for small numbers of phases. Given this and given that the optimal designs we have computed tend to have less than about six phases, the unsolved problem of optimal phase ordering for the general case is not important at this point, even though it would be a very interesting topic to study.

Because the optimization routine we used does not directly account for the requirement that two of our parameters number of phases and number of turns—can only take on integer values, the optimization proceeds in three stages. First, for any give number of phases, the design is optimized based on allowing non-integer numbers of turns. Then, from those results, we select the closest integer number, and repeat the optimization with the number of turns fixed at that integer value. Finally, from a list of the results with different numbers of phases, we can select the result with the best performance. Table III summarizes the design details and performance for different numbers of phases.

The results in Table III show that any of the numbers of phases considered achieve very good performance when the inductor design and operating frequency are optimized. The minimum loss is achieved with four phases, and it has about 7% lower loss than the two-phase coupled system. Perhaps more important than this reduction in overall loss is the 15 to 19% reduction in silicon loss that the four- to six-phase designs provide relative to the two-phase configuration. This could allow using smaller MOSFETs, reducing cost.

An uncoupled multiphase converter with the same response time, and with the switching frequency optimized for minimum MOSFET losses (considering gate drive and conduction loss), would have 17.2 W of MOSFET loss, and would operate at 872 kHz. The total loss would depend on the details of the inductor design, which would entail significant ac resistance effects that we did not consider in this coupled inductor design, so we have not compared the overall loss of the coupled and uncoupled designs. However, just considering total MOS-FET loss (which is 84% of the loss in the optimized coupled four-phase design), the optimized coupled four-phase design cuts this loss to 11.9 W, a 31% reduction compared to the uncoupled design. The loss reduction comes from reduced ripple and from reduced switching frequency. We have used the same low-gate-charge MOSFETs for all the analysis, but the lower switching frequency of the coupled design relaxes the requirement for low gate charge and so could make it possible to use other MOSFETs that may be less expensive or have lower on-resistance.

One way to evaluate the performance of this coupled inductor design is to compare its performance to a theoretical limit: the MOSFET loss with the same MOSFETs carrying only the dc current with zero ripple, switching at such a low frequency that switching losses are negligible. In this case, the MOSFETs we have selected would have 9.64 W of loss. The total MOSFET loss in the uncoupled design is 78% above this hypothetical theoretical minimum loss, whereas the optimized four-phase design has only 23% more loss than the theoretical minimum. This means that the four-phase coupled design has already achieved most of the loss reduction that is theoretically possible by any means, using this same fixed FET technology.

It is important to note the improvements come from changing only the inductor structure. No additional components or other changes are needed in the rest of the power circuit, which remains a standard multiphase buck converter, the same as would be used without coupling.

### VI. EXPERIMENTAL VERIFICATION

Basic operation and ripple reduction as predicted have been verified in open-loop steady-state operation with nonoptimized coupled inductors, both two-phase and four-phase (the latter in the ladder configuration). In anticipation of further experiments with an improved prototype and optimized designs, detailed waveforms were not recorded in these initial experiments. Unfortunately, the new prototype was not ready in time for this paper.

## VII. CONCLUSION

Coupled inductors can be used to obtain dramatic performance improvements in multiphase buck converters with requirements for fast response time. A new topology for multiphase (more than two phases) coupled inductors allows practical operation with much stronger coupling than is possible with previous multiphase coupled inductor topologies. The circuit topology aside from the inductors is a standard multiphase buck topology, identical to that used with uncoupled inductors. Optimization of the complete system including the inductor geometry and switching frequency shows that the best performance can be obtained with four coupled phases, for the particular parameters considered in this optimization. This provides a reduction in MOSFET losses by 31% compared to an uncoupled design with the same response time.

#### REFERENCES

- B. Rose, "Voltage regulator technology requirements", in 4th Annual Intel Technology Symposium, Sept. 1990.

- [2] G. Schuellein, "Current sharing of redundant synchronous buck regulators powering high performance microprocessors using the V<sup>2</sup> control method", in *Thirteenth Annual Applied Power Electronics Conf. and Exposition*, 1998, vol. 2, pp. 853–9.

- [3] A.M. Wu, Jinwen Xiao, D. Markovic, and S.R. Sanders, "Digital PWM control: application in voltage regulation modules", in 30th Annual IEEE Power Electronics Specialists Conf., 1999, pp. 77–83 vol.1.

- [4] Jinwen Xiao, A.V. Peterchev, and S.R. Sanders, "Architecture and IC implementation of a digital VRM controller", in 32nd Annual IEEE Power Electronics Specialists Conf., 2001.

- [5] Xunwei Zhou, Pit-Leong Wong, Peng Xu, F.C. Lee, and A.Q. Huang, "Investigation of candidate VRM topologies for future microprocessors", *IEEE Trans. on Power Electronics*, vol. 15, no. 6, pp. 1172–82, 2000.

- [6] G.J. Mehas, K.D. Coonley, and C.R. Sullivan, "Converter and inductor design for fast-response microprocessor power delivery", in *Proceedings of the 31st Annual Power Electronics Specialist Conf.*, 2000, pp. 1621–6 vol.3.

- [7] R. Miftakhutdinov, "Optimal design of interleaved synchronous buck converter at high slew-rate load-current transients", in 32nd Annual Power Electronics Specialists Conf., 2001.

- [8] Pit-Leong Wong, Q. Wu, Peng Xu, Bo Yang, and F.C. Lee, "Investigating coupling inductors in the interleaving QSW VRM", in *Proceedings* of APEC 2000 - Applied Power Electronics Conf., pp. 973–8 vol.2.

- [9] Pit-Leong Wong, Peng Xu, P. Yang, and F.C. Lee, "Performance improvements of interleaving VRMs with coupling inductors", *IEEE Trans. on Power Electronics*, vol. 16, no. 4, pp. 499–507, 2001.

- [10] P.-L. Wong, F.C. Lee, X. Jia, and D. Van Wyk, "A novel modeling concept for multi-coupling core structures", in *Proceedings of 16th Annual Applied Power Electronics Conf.*, 2001, pp. 102–8 vol.1.

- [11] W. Huang, "A new control for multi-phase buck converter with fast transient response", in *Proceedings of 16th Annual Applied Power Electronics Conf.*, 2001, pp. 273–279, vol.1.

- [12] G. Capponi, L. Minneci, F. Librizzi, and P. Scalia, "Multiphase voltage regulator module with transient step changing phases", in *Proceedings* of the International Conference on Power System Technology, Power-Con 2000, 2000, pp. 463–467 vol.1.

- [13] J. G. Kassakian, Martin F. Schlecht, and George C. Verghese, *Principles of Power Electronics*, Addison Wesley, 1991.

- [14] E. C. Snelling, Soft Ferrites, Properties and Applications, Butterworths, second edition, 1988.

- [15] J. Reinert, A. Brockmeyer, and R.W. De Doncker, "Calculation of losses in ferro- and ferrimagnetic materials based on the modified Steinmetz equation", in *Proceedings of 34th Annual Meeting of the IEEE Industry Applications Society*, 1999, pp. 2087–92 vol.3.

- [16] Jieli Li, T. Abdallah, and C.R. Sullivan, "Improved calculation of core loss with nonsinusoidal waveforms", in *IEEE Industry Applications Society Annual Meeting*, 2001, pp. 2203–2210.

- [17] J.C. Lagarias, J.A. Reeds, M.H. Wright, and P.E. Wright, "Convergence properties of the Nelder-Mead simplex method in low dimensions", SIAM Journal on Optimization, vol. 9, no. 1, pp. 112–47, 1998.